ISE Proyect Navigator

Objetivos

- Aprender a usar el ISe Project Navigator como una herramienta de software en que apoye en el aprendizaje de la tecnología de lógica no cableada en circuitos digitales.

- Poder desarrollar el procedimiento de edición o captura, verificación funcional, rutado y conexionado.

- Poder simular circuitos digitales usando el software de simulación ISE Project Navigator.

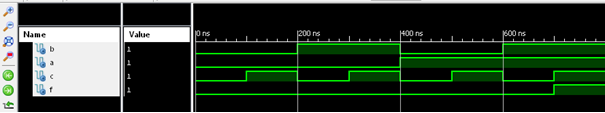

- Analizar he interpretar los resultados de la simulación en un diagrama de tiempo.

Introducción Teórica

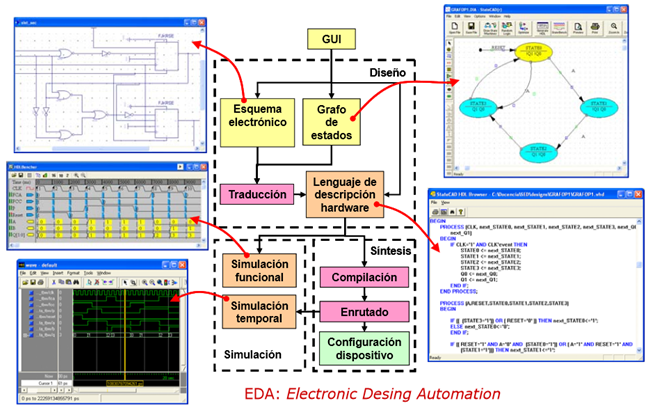

El proceso de diseño se llevará a cabo a través de los pasos indicados en la figura 1, que se describen brevemente a continuación.

Create Code/Schematic:El diseño debe ser introducido en la herramienta mediante la ubicación y conexionado de los diferentes componentes, disponibles en varias bibliotecas

Funcional Simulation:Permite comprobar que la funcionalidad del esquema capturado es la esperada. Para ello deben especificarse los valores que deben colocarse en las entradas del circuito (mediante el fichero scf), a continuación, debe simularse el periodo de tiempo deseado, y finalmente debe comprobarse que los resultados en las salidas del circuito sean correctos.

Place and Route:Si la simulación del circuito ha sido satisfactoria, el siguiente paso consiste en ubicar el diseño en el chip programable del que se disponga (en nuestro caso el chip EPM7128SLC84). Para ello debe compilarse el diseño, de manera que se asignarán las puertas que lo componen a las celdas programables de las que dispone el chip y se decidirá su interconexión. Como resultado de esta etapa se obtendrá el fichero de programación del chip

Programming:Una vez obtenido el fichero de programación correspondiente al diseño, debe conectarse el cable de programación (byteblaster) al puerto paralelo del PC y la placa de demostración. Mediante la programación el contenido del fichero será transferido a la placa. Si la programación se ha realizado correctamente podremos comprobar cómo efectivamente, a cada pulsación de uno de los botones de la placa, ésta cuenta.

Procedimiento

I. Primera parte

A continuación, se detallan los pasos que, siguiendo el diagrama de flujo indicado en la figura 1, permitirán completar el diseño del proyecto.

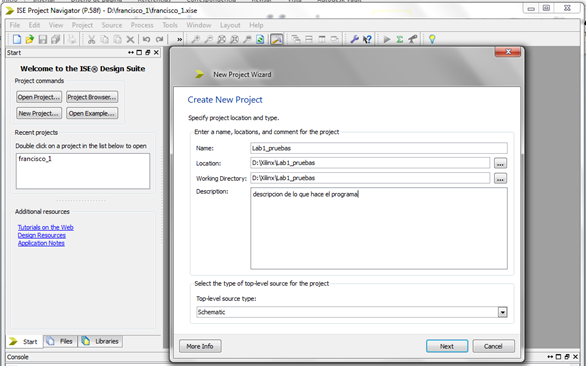

Lanzar el programa ISE Project Navigator

Creación del nuevo proyecto

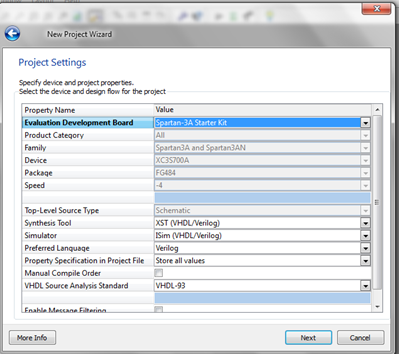

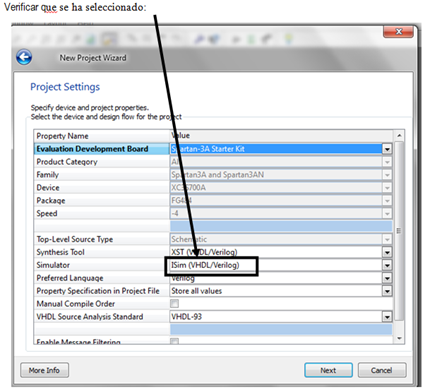

Puesto que la captura del diseño va a realizarse mediante un esquemático crea un nuevo Proyecto con el Project Wizard

Escoger el TOP-LEVEL SOURCE TYPE: Schematic

Clickear en "next" y seleccionar Evaluation Development Board Spartan-3A Starter Kit Spartan 3A and Spartan3AN:

Tras hacer Next y después Finish terminamos de poner los diferentes parámetros del gestor de proyectos.

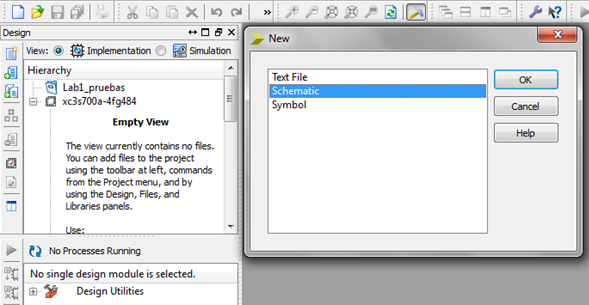

La siguiente etapa es clickear New y escoger Schematic

Como resultado se abre un nuevo esquemático de nombre "untitledSchematic1.sch".

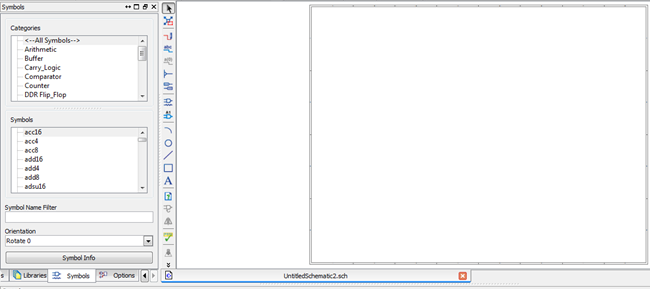

Se hace click en la pestaña marcada Symbols para que parezca a la izquierda una lista de símbolos que podremos utilizar.

Captura del esquema

Para añadir un nuevo componente al esquema debe realizar un click sobre el símbolo deseado

Selecciona los diferentes componentes que forman parte del esquemático.

Puedes replicar los componentes tantas veces como quieras seleccionando una instancia, copiándola en el portapapeles (ctrl + C) y pegándola de nuevo (ctrl + V)

Conecta los componentes a los diferentes módulos y pines de entrada y salida.

Haz un clic derecho sobre la etiqueta de cada pin, y reemplázala por el nombre que le corresponda.

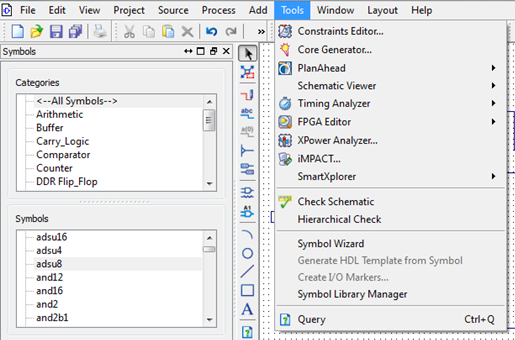

Graba con el nombre "monigote" y verifica el esquematico Tools --> Check Schematic

Si el esquema es correcto el compilador lo notificará con el mensaje '0 errors and 0 warnings'.

Si se han producido errores se abrirá una nueva ventana con información detallada. Para acceder al punto donde se localiza el error haz doble click sobre cada mensaje. Corrige todos los errores y repite la verificación.

Cuando nos ponemos en la etiqueta y miramos sus propiedades que vemos como propiedades

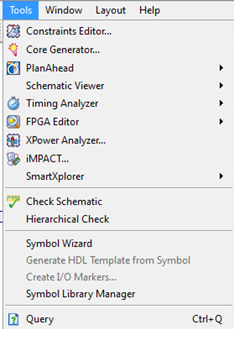

Ir a tools y anotar todo lo que tenemos con una Breve descripción de lo que hacen.

Desarrollo

- Library ieee;

- Use ieee.srd_logic_1164.ALL;

- Use ieee.numeric_std.ALL;

- library UNISIM;

- Use UNISIM.Vcomponents.ALL;

- ENTITY Ejemplo01_Ejemplo01_sch_tb IS

- END Ejemplo01_Ejemplo01_sch_tb;

- ARCHITECTURE behavioral OF Ejemplo01_Ejemplo01_sch_

- COMPONENT Ejemplo01

- PORT( B : IN STD_LOGIC;

- A : IN STD_LOGIC;

- C : IN STD_LOGIC;

- F : OUT STD_LOGIC);

- END COMPONENT;

- SIGNAL B : STD_LOGIC;

- SIGNAL A : STD_LOGIC;

- SIGNAL C : STD_LOGIC;

- SIGNAL F : STD_LOGIC;

- BEGIN

- UUT: Ejemplo01 PORT MAP(

- B => B,

- A => A,

- C => C,

- F => F

- );

- --*** Test Bench - User Defined Section ***

- tb : PROCESS

- BEGIN

- A <= '0';

- B <= '0';

- C <= '0';

- wait for 100ns;

- A <= '0';

- B <= '0';

- C <= '1';

- wait for 100ns;

- A <= '0';

- B <= '1';

- C <= '0';

- wait for 100ns;

- A <= '0';

- B <= '1';

- C <= '1';

- wait for 100ns;

- A <= '1';

- B <= '0';

- C <= '0';

- wait for 100ns;

- A <= '1';

- B <= '0';

- C <= '1';

- wait for 100ns;

- A <= '1';

- B <= '1';

- C <= '0';

- wait for 100ns;

- A <= '1';

- B <= '1';

- C <= '1';

- wait for 100ns;

- WAIT; --will wait forever

- End PROCESS;

- --*** End Test Bench - User Defined Section ***

- END;

- Library ieee;

- Use ieee.srd_logic_1164.ALL;

- Use ieee.numeric_std.ALL;

- library UNISIM;

- Use UNISIM.Vcomponents.ALL;

- ENTITY ejemesq_ejmesq_sch_sch_tb IS

- END ejmesq_ejmesq_sch_tb;

- ARCHITECTURE behavioral OF ejmesq_ejmesq_sch_tb IS

- COMPONENT ejmesq

- PORT ( A : IN STD_LOGIC;

- CLK : IN STD_LOGIC

- Q1 : OUT STD_LOGIC;

- Q0 : OUT STD_LOGIC;

- CLR : IN STD_LOGIC);

- END COMPONENT;

- SIGNAL A: STD_LOGIC;

- SIGNAL CLK: STD_LOGIC;

- SIGNAL Q1: STD_LOGIC;

- SIGNAL Q0 : STD_LOGIC;

- SIGNAL CLR : STD_LOGIC;

- BEGIN

- UTT: ejmesq PORT MAP(

- A => A,

- CLK => CLK,

- Q1 => Q1,

- Q0 => Q0,

- CLR => CLR

- );

- -- *** Test Bench - User Defined Section ***

- tb : PROCESS

- BEGIN

- A <= '0';

- CLK <='0';

- CLR <= '1';

- wait for 100ns;

- A <= '1';

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- A <= '1';

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- wait; --will wait forever

- END PROCESS;

- -- *** End Test Bench - User Defined Section ***

- END;

- Library UNISIM;

- USE UNISIM.Vcomponents.ALL;

- ENTITY Ejemplo04_Ejemplo04_sch_tb IS

- END Ejmeplo04_Ejemplo04_sch_tb;

- ARCHITECTURE behavioral OF Ejemplo04_Ejemplo04_sch_tb Is

- COMPONENT Ejemplo04

- PORT ( Q2 : OUT STD_LOGIC;

- Q0 : OUT STD_LOGIC;

- Q1 : OUT STD_LOGIC;

- CLK : IN STD_LOGIC;

- CLR : IN STD_LOGIC);

- END COMPONENT;

- SIGNAL Q2 : STD_LOGIC;

- SIGNAL Q0 : STD_LOGIC;

- SIGNAL Q1 : STD_LOGIC;

- SIGNAL CLK : STD_LOGIC;

- SIGNAL CLR : STD_LOGIC;

- BEGIN

- UTT: Ejemplo04 PORT MAP(

- Q2 => Q2,

- Q0 => Q0,

- Q1 => Q1,

- CLK => CLK,

- CLR => CLR

- );

- --*** Test Bench - User Defined Section ***

- tb : PROCESS

- BEGIN

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- CLK <= '0';

- CLR <= '0';

- wait for 100ns;

- CLK <= '1';

- CLR <= '0';

- wait for 100ns;

- CLK <= '1';

- CLR <= '1';

- wait for 100ns;

- WAIT; -- will wait forever

- END PROCESS;

- -- *** End Test Bench - User Defined Section ***

- END;

II. Segunda parte

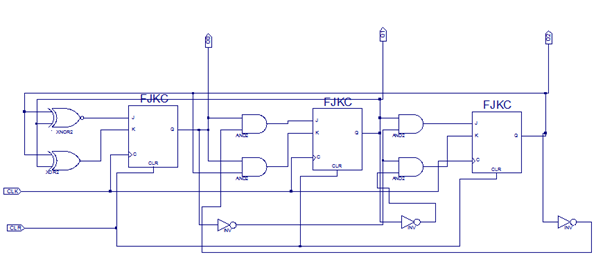

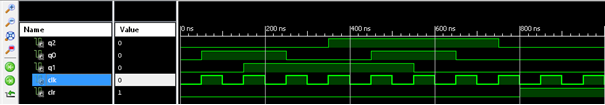

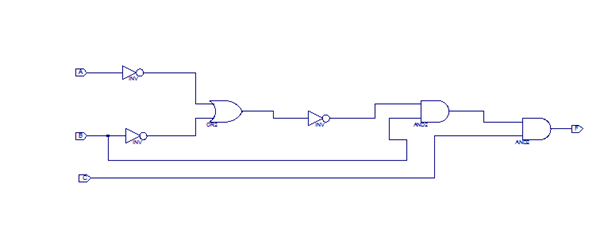

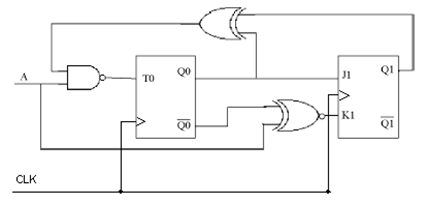

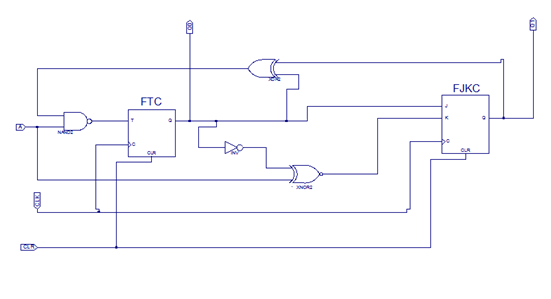

Usando el procedimiento mostrado en la parte I, realice todos los pasos para crear y simular un proyecto, para el siguiente circuito y compruebe los resultados con el diagrama de tiempos realizado teóricamente.

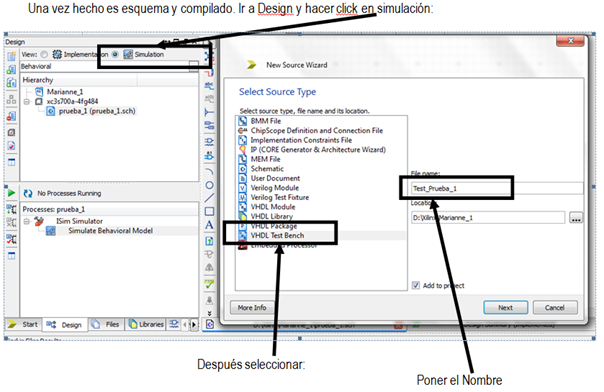

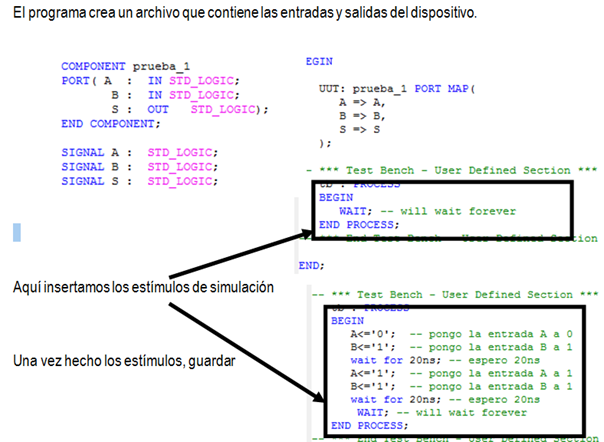

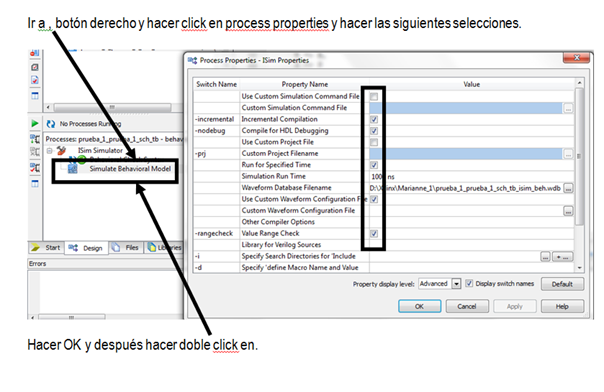

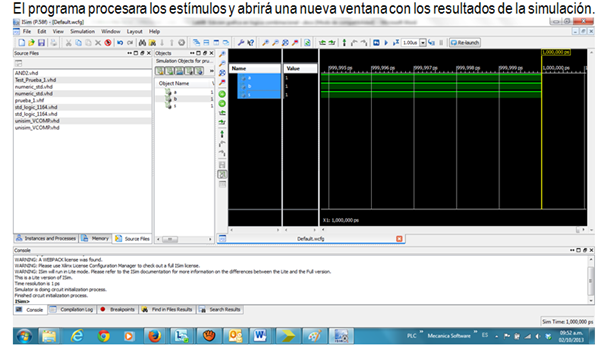

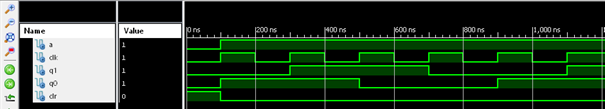

La parte Simulación se desarrolla de la siguiente manera:

Repetimos los estímolos tantas veces que sea necesario.

Siendo las entradas las líneas A y CLK y las salidas Q1 y Q0.

Hagan el esquemático y muestren su diagrama de tiempos.

Implemente el siguiente contador