Edición gráfica en lógica secuencial

Introducción

Las máquinas de estado finito FSM, representan una técnica especial de modelado de circuitos lógicos secuenciales; esta conceptuación es de extremada utilidad en el diseño de circuitos donde todas sus funciones pueden ser exactamente listadas, conteniendo todos los posibles estados y sus condiciones para que estos evoluciones de uno a otro estado, con el desarrollo de los sistemas embebidos y su cada vez mayor velocidad, las máquinas de estado finito se han convertido en una poderosa herramienta para el desarrollo de controladores digitales.

Existen dos representaciones fundamentales de las FSM una relacionada con sus especificaciones llamada diagrama de transición de estados y otra relacionada al hardware conocida como de lógica combinacional/secuencial.

Durante esta entrada se brindara los fundamentos de estas técnicas de modelado, la forma como codificar las FSM con lenguaje VHDL y su implementación en los FPGA.

Para diseñar usando FSM el primer paso fundamental es la declaración de todos los posibles estados en los que puede caer el circuito a diseñar, estos se pueden listar, declarando un nombre corto del estado, la salida que debe reflejar en el momento de llegar a él y por supuesto la funciones de evolución de estados, con esta información ya podemos desarrollar una representación formal de la máquina.

Objetivos

- Poder desarrollar circuitos digitales usando la herramienta de captura esquemática del software de simulación Max Plus II en Lógica secuencial.

- Poder simular circuitos digitales usando el software de simulación Max Plus II

- Analizar he interpretar los resultados de la simulación.

Procedimiento

Primera parte

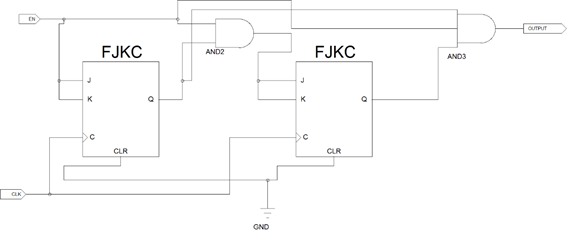

Analice la máquina de estados síncrona temporizada en la figura 3.

Escriba las ecuaciones de excitación (lógica de estado siguiente), la tabla de excitación/transición (tabla de estado actual/siguiente), y la tabla de estadas/salidas (utilice los nombre de estado A-D para Q1Q0=00-11).

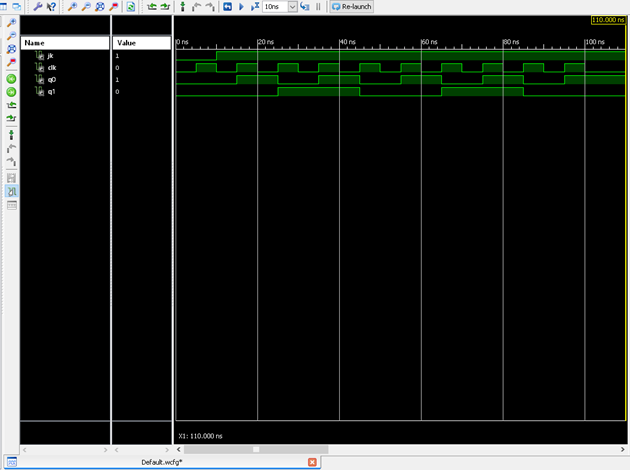

Dibuje el diagrama de estados y trace un diagrama de temporización para CLK, EN, Q1 y Q0 para los 10 tics de reloj, suponiendo que la máquina comienza en el estado 00 y EN es continuamente 1.

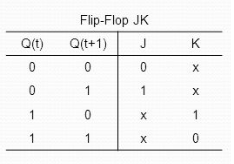

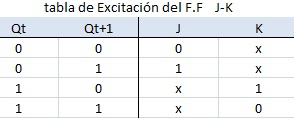

Tabla de excitación del flip flop JK

Tabla de excitación del flip flop JK

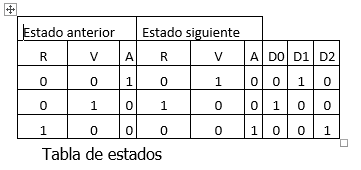

Tabla de estados

Tabla de estados

- --Revision 0.01 - File Created

- --Additional Comments:

- --

- ------------------------

- LIBRARY IEEE;

- Use ieee.std_logic_1164.ALL;

- entity contador0a3 is

- port(jk, clk: in std_logic;

- q1, q0: inout std_logic

- );

- end contador0a3;

- architecture cuenta of contador0a3 is

- begin

- process (jk,clk)

- begin

- if (jk='1' and clk='1' and q0='0' and q1='0') then

- q1<='0';

- q0<='1';

- elsif (jk='1' and clk='0' and q0='1' and q1='0') then

- q1<='0';

- q0<='1';

- elsif (jk = '1' and clk='1' and q0='1' and q1='0') then

- q1<='1';

- q0<='0';

- elsif (jk='1' and clk='0' and q0='0' and q1='1') then

- q1<='1';

- q0<='0';

- elsif (jk='1' and clk='1' and q0='0' and q1='1') then

- q1<='1';

- q0<='1';

- elsif (jk='1' and clk='1' and q0='1' and q1='1') then

- q1<='0';

- q0<='0';

- else

- q1<='0';

- q0<='0';

- end if;

- end process;

- end cuenta;

- BEGIN

- --Instantiate the unit Under Test (UUT)

- uut: contador0a3 PORT MAP (

- jk => jk,

- clk=> clk,

- q1 =>q1,

- q0 => q0

- );

- -- Stimulus process

- stim_proc: process

- begin

- jk<='0';

- clk<='0'

- wait for 10ns;

- jk<='1';

- clk<='0'

- wait for 10ns;

- jk<='1';

- clk<='1'

- wait for 10ns;

- jk<='1';

- clk<='0'

- wait for 10ns;

- jk<='1';

- clk<='1'

- wait for 10ns;

- jk<='1';

- clk<='0'

- wait for 10ns;

- jk<='1';

- clk<='1'

- wait for 10ns;

- jk<='1';

- clk<='0'

- wait for 10ns;

- jk<='1';

- clk<='1'

- wait for 10ns;

- jk<='1';

- clk<='0'

- wait for 10ns;

- wait;

- end process;

- END;

Segunda parte:

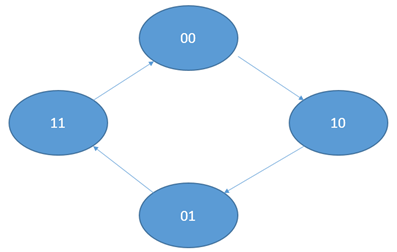

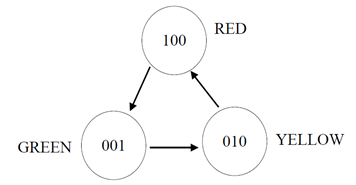

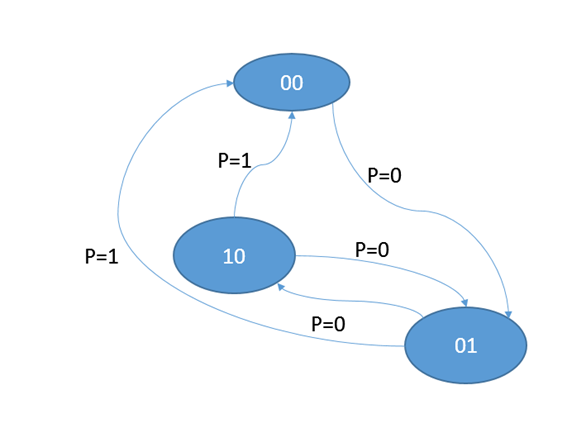

El Siguiente diagrama de estados corresponde a un control de luces para un semáforo, el cual presenta un diagrama de estados como el que se muestra:

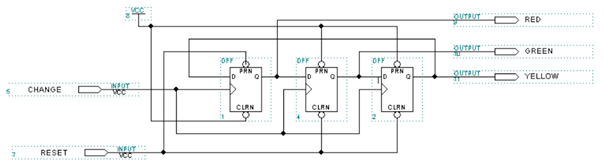

Este diagrama de estados se representa mediante el siguiente circuito:

Se pide:

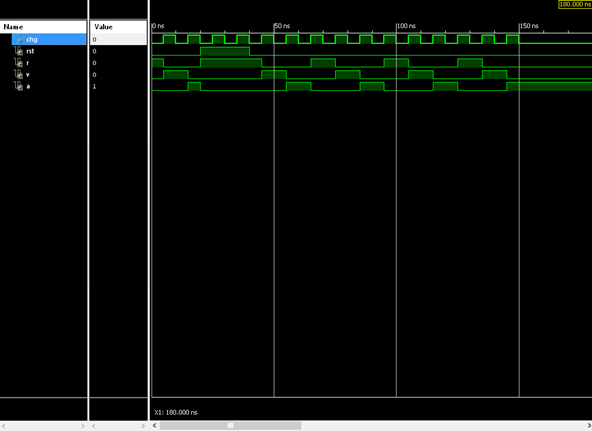

- Obtenga el diagrama de tiempos de circuito

- Diga si el diagrama de estados corresponde al circuito.

- Determine la tabla de diseño o transición de la máquina de estados que dio origen al circuito.

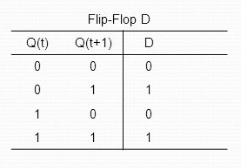

Tabla de excitación del flip flop tipo D

Tabla de excitación del flip flop tipo D

El diagrama de estados corresponde al circuito, se puede verificas en el diagrama de tiempo. También se comprobó mediante el uso de multisom.14

- -- Stimulus process

- stim_proc: process

- begin

- CHG<='0';

- RST<='0'

- wait for 10ns;

- CHG<='1';

- RST<='0'

- wait for 10ns;

- CHG<='0';

- RST<='1'

- wait for 10ns;

- CHG<='1';

- RST<='1'

- wait for 10ns;

- CHG<='1';

- RST<='0'

- wait for 10ns;

- CHG<='0';

- RST<='0'

- wait for 10ns;

- CHG<='1';

- RST<='0'

- wait for 10ns;

- CHG<='0';

- RST<='0'

- wait for 10ns;

- CHG<='1';

- RST<='0'

- wait for 10ns;

- CHG<='0';

- RST<='0'

- wait for 10ns;

- CHG<='1';

- RST<='0'

- wait for 10ns;

- CHG<='0';

- RST<='0'

- wait for 10ns;

- wait;

- end process;

- END;

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- entity semaforo is

- port (CHG,RST: in std_logic;

- R,V,A: inout std_logic

- );

- end semaforo;

- architecture semaforo is

- begin

- process (CHG,RST)

- begin

- if (CHG='1' and RST='0' and R='1' and A='0' and v='0') then

- R<='0';

- V<='1';

- A<='0';

- if (CHG='0' and RST='0' and R='0' and A='0' and v='1') then

- R<='0';

- V<='1';

- A<='0';

- if (CHG='1' and RST='0' and R='0' and A='0' and v='1') then

- R<='0';

- V<='0';

- A<='1';

- if (CHG='0' and RST='0' and R='0' and A='1' and v='0') then

- R<='0';

- V<='0';

- A<='1';

- else

- R<='1';

- V<='0';

- A<='0';

- end if;

- end process;

- end rgb;

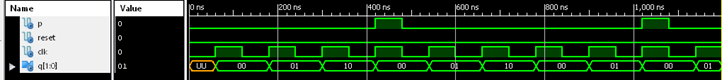

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- entity aplication12 is

- port(

- P: in std_logic;--PASAR

- reset: in std_logic;

- clk:in std_logic;

- Q: inout std_logic_vector (1 downto 0)

- );

- end aplication12;

- architecture app12 of aplication12 is

- begin

- process (P,reset,clk)

- begin

- if(reset='1') then

- Q<="00";

- elsif (clk'event and clk='1') then

- if(Q="00" and P='0') then

- Q<="01";

- elsif(Q="01" and P='0')then

- Q<="10";

- elsif (Q="01" and P='1')then

- Q<="00";

- else

- Q<="00";

- end if;

- end if;

- end process;

- end app12

- library IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- entity aplication12_tb is

- end aplication12_tb;

- architecture behavior of aplication12_tb is

- component aplication12

- port(

- p: un std_logic;

- reset: in std_logic;

- clk: in std_logic;

- q: inout std_logic_vector(1downto 0)

- );

- end component;

- signal p: std_logic :='0';

- signal reset: std_logic:='0';

- signal clk: std_logic :='0';

- signal q: std_logic_vector(1 downto 0);

- begin

- utt: aplication12 port MAP(

- p => P,

- reset => reset,

- clk => clk,

- Q=> Q

- );

- -- Stimulus process

- stim_proc: process

- begin

- clk<='0';

- p<='0'

- reset<='0';

- wait for 60ns;

- clk<='1';

- p<='0';

- reset<='0';

- wait for 60ns;

- clk<='0';

- p<='0'

- reset<='0';

- wait for 60ns;

- clk='1';

- p<='0'

- reset<='0'

- wait for 60ns;

- clk<='0';

- p<='0'

- reset<='0'

- wait for 60ns;

- clk<='1';

- p<='0'

- reset<='0'

- wait for 60ns; --

- clk<='1';

- p<='1'

- reset<='0';

- wait for 60ns;

- clk<='0';

- p<='0'

- reset<='0';

- wait for 60ns;

- clk<='1';

- p<='0'

- reset<='0';

- wait for 60ns;

- wait;

- end process;

- END;

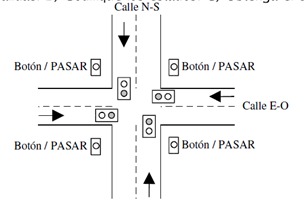

Aplicación de lo aprendido

Diseñe un controlador de semáforos simplificado que conmute las luces de un cruce de calles ( calle Norte-Sur N-S y calle Este-Oeste E-O). La entrada del controlador es un botón llamado PASAR que es activado por los peatones cuando desean cruzar alguna de las calles. Las salidas del controlador son dos señales, N-S y E-o, para las cuales el valor 0 indica luz roja y el valor 1 indica luz verde. Si no hay peatones, N-S=0 y E-O=1 durante 1 minuto, para luego cambiar a N-S=1 y E-O=0 por el mismo lapso de tiempo y repetir la secuencia anterior. Cuando se pulsa PASAR, N-S y E-O se colocan a 0 durante 1 minuto, siempre que el minuto actual haya concluido. Después de esto, las señales N-S y E-O contin+uan alternándose. Se pide: A)Desarrolle un diagrama de estados y una tabla de estados/salidas. B) Codifique los estados. C) Obtenga el circuito lógico asociado.

Pueden descargar los archivos de ISE desde el siguiente enlace:https://github.com/mokuzaru/vhdl_labs