Intermedio > Circuitos integrados > Diseño jerarquico II

Diseño jerarquico II

Diseño jerarquico

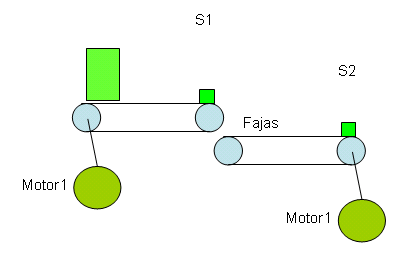

1. Realice el diseño para la sincronización de movimiento de dos fajas que transportan cajas en función de dos sensores colocados como se muestra en la figura

Los motores tienen como mando las líneas de Start/Stop y de Cambio de sentido de Giro

La condición es que por criterios de ahorro de nergía las fajas no deben de moverse si no estan transportando cajas.

- Realizar el diagrama de bloques

- Indicar la función lógica realizada por cada bloque

- Diseñar cada bloque, implementar mediante el Max Plus. Depurar simular cada bloque

- integrar todo en un diseño jerárquico

- Definir las entradas y salidas y la configuración de pines en el integrado

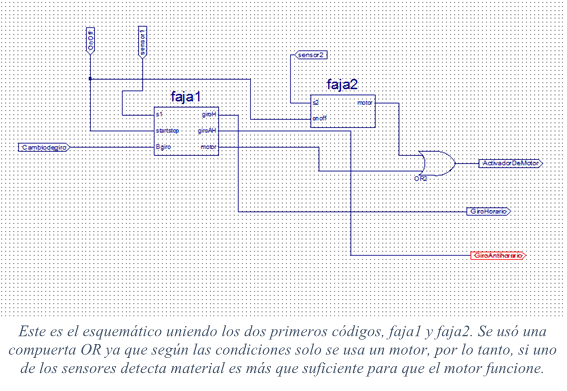

usaremos dos bloques, uno llamado faja 1, el otro llamado faja2. Ambos tendrán el mismo activador, sin embargo solo el primero tendrá la salida de cambio de giro.

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- entity faja1 is

- port(s1: in std_logic;--sensores

- startstop: in std_logic;--0_Stop; 1:Start

- Bgiro: in std_logic;--0:Giro horario; 1:Giro antihorario

- giroH,giroAH,motor: out std_logic);

- end faja1;

- arquitecture faja0 of faja1 is

- begin

- process (s1,startstop,Bgiro)

- begin

- if(startstop='1' and s1='1' and Bgiro='0') then

- motor<='1';

- giroH<='1';

- giroAH<='0';

- elseif (startstop='1' and s1='1' and Bgiro='1') then

- motor<='1';

- giroH<='0';

- giroAH<='1';

- else

- motor<='0'

- giroH<='0'

- giroAH<='0'

- end if;

- End process;

- end faja0;

Código en VHDL

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- entity faja2 is

- port (s2: in std_logic;--sensor

- onoff: in std_logic; --activador

- motor: out std_logic);

- end faja2;

- architecture fajita of faja2 is

- begin

- process (s2,onoff)

- begin

- if (onoff='1' and s2='1') then

- motor<='1';

- else

- motor<='0';

- end if;

- end process;

- end fajita;

- LIBRARY IEEE;

- Use ieee.std_logic_1164.ALL;

- USE ieee.numeric_std-ALL;

- LIBRARY UNISIM;

- USE UNISIM.Vcomponents.ALL;

- entity lab15_lab_sch_tb is

- END lab15_lab_sch_tb;

- architectur behavioral of homework is

- COMPONENT lab15

- PORT( OnnOff : IN STD_LOGIC;

- Cambiogiro : IN STD_LOGIC;

- sensor1 : IN STD_LOGIC;

- sensor2 : In STD_LOGIC;

- girohorario : OUT STD_LOGIC

- giroantihorario : OUT STD_LOGIC;

- MotorOn : OUT STD_LOGIC);

- EN COMPONENT;

- SIGNAL OnOff : STD_LOGIC;

- SIGNAL Cambiogiro : STD_LOGIC;

- SIGNAL sensor1: STD_LOGIC;

- SIGNAL sensor2: STD_LOGIC

- SIGNAL girohorario : STD_LOGIC

- SIGNAL giroantihorario : STD_LOGIC

- SIGNAL MotorOn : STD_LOGIC

- Begin

- UUT: lab15 PORT MAP(

- OnOff => OnOff,

- Cambiogiro => Cambiogiro,

- sensor1 => sensor1,

- sensor2 => sensor2,

- girohorario=>girohorario,

- giroantihorario=>giroantihorario,

- MotorOn=>MotorOn,

- );

- -- *** Test Bench - User DEfine Section****

- tb:Process

- BEGIN

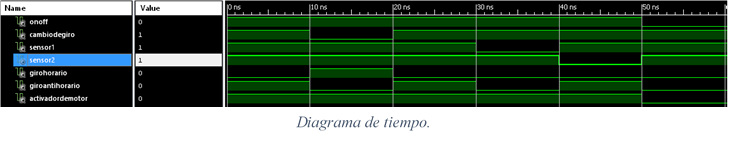

- onoff<='1';

- cambiogiro<='1';

- sensor1<='1';

- sensor2<='1';

- wair for 10ns;

- onoff<='1';

- cambiogiro<='0';

- sensor1<='1';

- sensor2<='1';

- wait for 10ns;

- onoff<='1';

- cambiogiro<='1';

- sensor1<='1';

- sensor2<='1';

- wait for 10ns;

- onoff<='1';

- cambiogiro<='1';

- sensor1<='0';

- sensor2<='1';

- wait for 10ns;

- onoff<='1';

- cambiogiro<='1';

- sensor1<='1';

- sensor2<='0';

- wait for 10ns;

- onoff<='0';

- cambiogiro<='1';

- sensor1<='1';

- sensor2<='1';

- wait for 10ns;

- WAIT; -- will wait forever

- END PROCESS;

- --***End Test Bench - User Defined Section ***

- END;

Pueden descargar los archivos de ISE desde el siguiente enlace:https://github.com/mokuzaru/vhdl_labs