Intermedio > Circuitos integrados > Diseño Jerarquico

Diseño Jerarquico

Objetivos

- Usar el VHDL como herramienta de edición de bloques funcionales a medida.

- Usar el VHDL en la edición mediante grafico y texto.

- Integrar bloques funcionales en sistemas de mayor complejidad usando diseño jerárquico.

- Asignación de pines al proyecto para su grabación.

Introducción Teórica

Preparación

Para el desarrollo de esta experiencia el alumno debe tener claro los conceptos dados en la clase teórica, revisar sus apuntes y afianzar sus conocimientos con el texto base y la bibliografía del curso

Problema

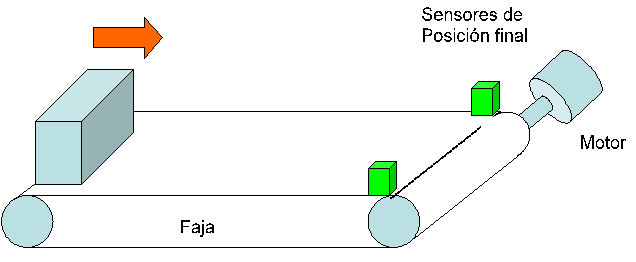

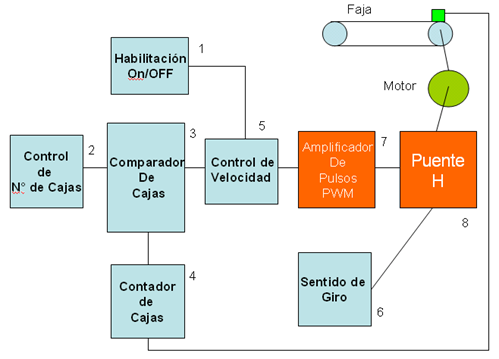

I. Se requiere realizar el diseño de un sistema que controle un motor el cual acciona una faja que transporta cajas como el que se muestra en la figura:

El sistema debe de tener los siguientes controles:

- Un interruptor de habilitación de todo el sistema.

- Un pulsador Start / Stop

- Controles de configuración de número de cajas, borrado de npumero de cajas

- Control para cambio el sentido de giro del motor

La estructura del sistema esta descrito mediante el sistema diagrama de bloques:

Procedimiento

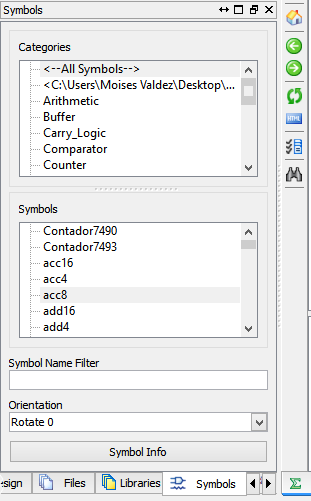

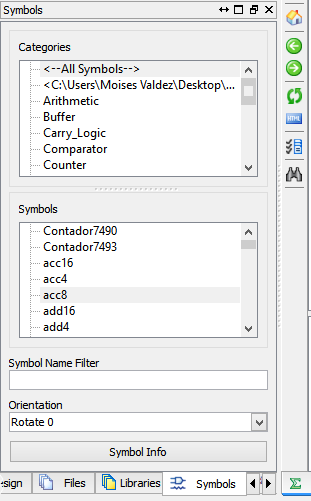

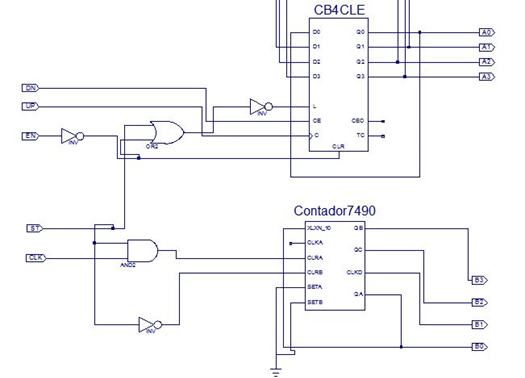

- Antes de comenzar a implementar los bloques, primero creamos un circuito lógico del 7490 y 7493 debido a que estos dos contadores no se encuentran en la librería de símbolos y es lo que se requiere.

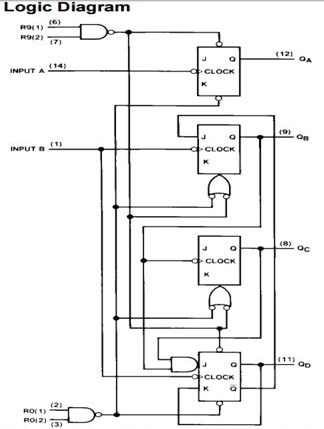

- Implementación del 7490

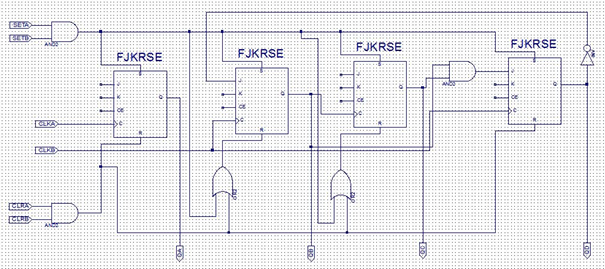

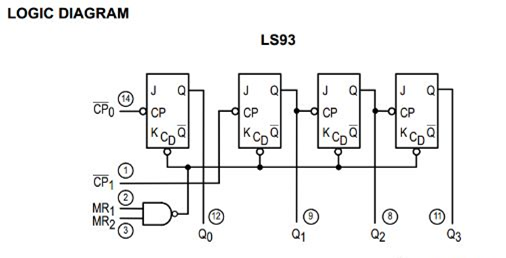

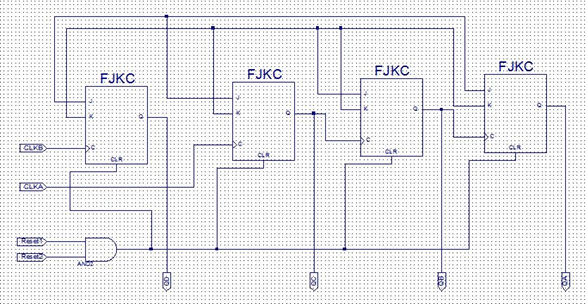

- Implementación del 7493

- Implementación del 7490

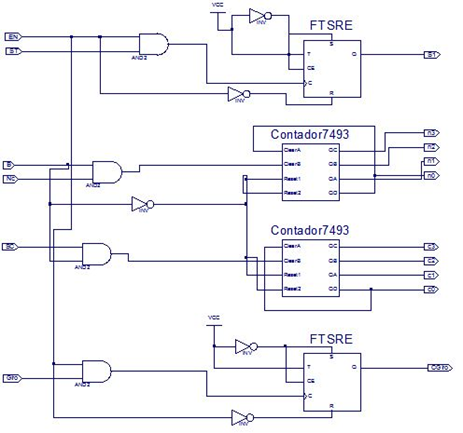

- Usando los contadores ya creados procedemos a implementar el primer bloque del proceso planteado.

- Código VHDL

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- entity Bloque2 is

- port(

- N, C: in std_logic_vector (3 downto 0);

- igual : out std_logic);

- end Bloque2;

- architecture behavioral of Bloque2 is

- begin

- process (N,C)

- begin

- if N=C then

- igual <='1';

- else

- igual <= '0';

- end if;

- end process;

- end behavioral;

- Implementando el tercer bloque

- Código VHDL

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- entity Bloque4 is

- port (

- A, B: in STD_LOGIC_VECTOR (3 downto 0);

- AmayorB : out STD_LOGIC);

- end Bloque4;

- architecture behavioral of Bloque4 is

- begin

- process (A,B)

- begin

- if A>B then

- AmayorB<='1';

- else

- AmayorB<='0';

- end if;

- end process;

- end behavioral;

- Una vez terminado el diseño de los bloques de la parte lógica. Realizar la integración de todo el sistema usando los archivos de librería antes editado. De acuerdo al siguiente diagrama:

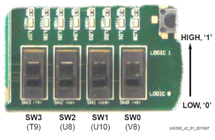

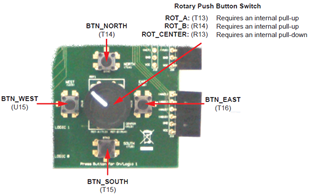

| Entradas | |

|---|---|

| Habilitación: | Interruptor |

| Start/Stop: | pulsador |

| Borrado: | Interruptor |

| NúmeroCajas: | pulsador |

| CajaSensadas: | Interruptor |

| SentidoGiro: | Interruptor |

| IncreVelocidad: | pulsador |

| DecreVelocidad: | pulsador |

| RelojModulador: |

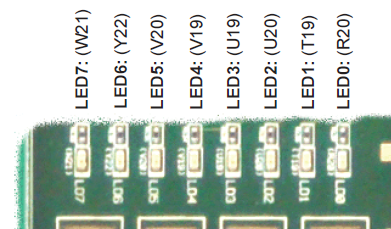

| Salidas: | |

|---|---|

| Ccomparación: | LED |

| Cgiro: | LED |

| SalidaModulador: | LED |

Los programas generados pueden ser descargados desde est link:https://github.com/mokuzaru/vhdl_labs